コンピュータの歴史を暗部も含めてていねいに掘り起こすことで定評のある大原雄介さんによる連載15回目。Intelにもこんなマイナープロセッサがあったのかということで、本連載初登場。DSPでもないAnalog Signal Processorです。

この連載でもちょこちょこDSP(Digital Signal Processor)の話をしていたと思うが、今回ご紹介するIntel 2920はそのDSPになり損ねた、ASP(Analog Signal Processor)である。

そもそもDSPとは何か? という話をする前に、まず何でDSP的なものを生み出す必要があったのか、について簡単に説明したい。

DSP的なものはなぜ必要とされたか

そもそもDSP的なものが要求された背景には、信号処理をデジタルで行いたい、というニーズがあった。

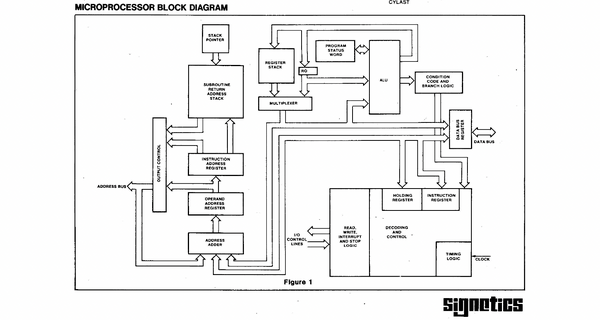

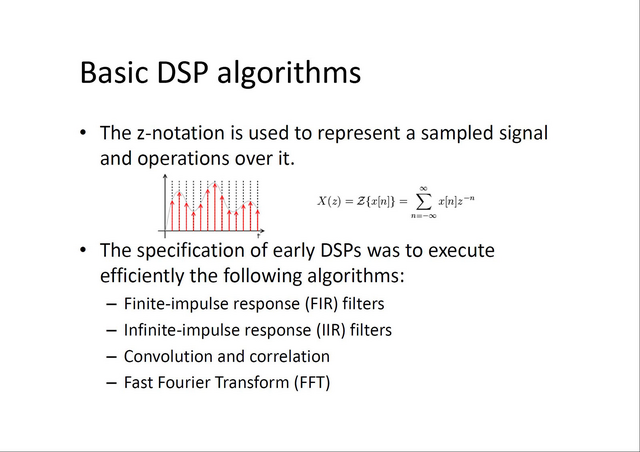

信号処理、最初に考案されていたのはフィルタとか畳み込み、それとFFTなどが目的だが、まず入力信号X(z) をZ変換を掛けてx[n] の数列にし、次いでこの数列に対して目的の処理を行い、最後に逆Z変換を掛ければ、処理を行った後の信号が生成されるということになる(Photo01)。

▲Photo01:これ数式で解くのは結構大変なのだが、Z変換は要するにADC、逆Z変換はDACを噛ませるだけの話なので、処理はフィルタリングやら畳み込みやらFFTやらだけを考えれば良いことになる

FIRフィルタとかIIRフィルタの詳細まで説明し始めると話がずれるので割愛するが、例えば電話(昨今の携帯電話でなく、昔の有線の電話機の話)だと会話で主に利用される300Hz~3.4kHzが伝達できれば問題なく、逆にここから外れる周波数の音(例えば自動車の排気音なら250Hz前後、騒音は一般に4kHz前後と言われる)を排除することで、明瞭に音声が伝わる様になる。

なので、300Hz~3.4kHzの音だけを通すようなフィルタを噛ませることでこれを実現しようとした。ここで利用されるのがBPF(Band Pass Filter)であるが、こうした機能はFIRやIIRフィルタの組み合わせで実現できる。あるいはサウンドイコライザーもこの一種だ。

「低音を盛り上げたい」とか「高音がちょっとシャリシャリ言うのでレベルを落としたい」とか、そういう目的で周波数帯ごとにレベルの上げ下げを行ったり、逆に周波数帯から分析を行う(騒音のピーク周波数から、例えばそれがモーターの騒音であれば回転数が推察できる)などの目的に利用されるが、これは信号にフーリエ変換を掛け、周波数別の信号強度を算出することで可能になる。

昔はこれを全部アナログ回路でやっていた訳だが、細かくやろうとすると回路規模が馬鹿でかくなり、コストも馬鹿にならないうえに信号劣化も激しくなる。またアナログが故に、精密な動作をするフィルタを構築するのは難しいなどの問題もある。

そこで、信号をまずADC(Analog-Digital Converter)で受けてデジタル化し、その後の処理を全部デジタルで行い、最後にDAC(Digital-Analog Converter)で再びアナログに戻せばよいのではないか? という考えに行き着くのはまぁ当然である。

さて、ここで問題になってくるのは「どうやってデジタル処理を行うのか」という話である。当たり前であるが、精度を高めるとそれだけデータ量が増える。

例えば音声を8bitでサンプリングするより16bitでサンプリングした方が、より原音に近い形でデジタル化できる。サンプリング頻度も高ければ高いほど、原音に近くなる。

初期のものだとADCの出力が8bit、サンプリング頻度22kHzとかだった訳だが、これだと毎秒あたり22KB/secのデータ量になる。これがもう少し精度の高い、例えばCDの音質だと16bit/44.1kHzのステレオなので、データ量は176.4KB/secになる。

このデータ量そのものは、何も加工しないで済むなら大した分量ではないのだが、これにフィルタリングを掛ける、という話になるとまた話が変わってくる。

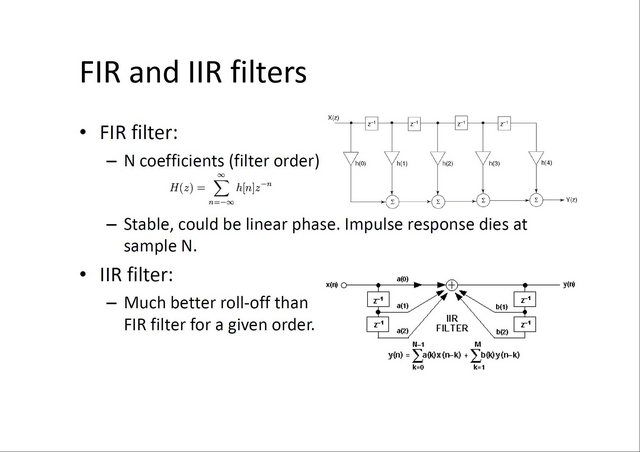

Photo02はFIR/IIRフィルタの基本的な考え方だが、例えば上側の5-TapのFIR Filterの場合でも常時5回の乗算と4回の加算が必要になる。

▲Photo02:このFIRの場合、h(n) が係数を持つ乗算器、Σが加算器、z^-1が遅延器となる

8bitモノラルで22.1kHzだとしても、加算が毎秒110K個、乗算が88K個必要になる。ここで加算は、精々110K個だから2~4MHzくらいの速度で動くCPUなら何とかなるのだが、問題は乗算の方である。

1978年に発表されたIntel 8086ですら、MUL(乗算)に要するCycle数は8bitで70~77cycleである(加算の方は8bitのReg→Regで3cycle)。だから仮に8086でこの5tapのFilter処理をやろうとすると、乗算と加算だけで毎秒7000Kcycle程必要になる。

つまり7MHz駆動で何とか間に合うかどうか。実際には入力を外部から受け取ったり、結果を外部に書き出す処理も入るから、10MHzでも間に合うかどうか、という辺りになる。

もっと言えば、加算にしても乗算にしても、整数演算だと不都合が多い。というのは特に掛け算のh(n)の方が、その係数というのが0.5とか0.03とか、小数になるのが普通なためだ。

もちろん方法はあって、例えば本来の数字の100倍(つまり係数は50とか3になる)で計算をして、最後に100で割るという方法は広く使われる(*1)。

*1:説明のために100倍とかにしたが、実際はこんな割り切りにくい数字ではなく、2のべき乗(例えば16とか)を使う。これだと乗除算がシフト演算で行えるので簡単かつ高速になる

ただこの場合、今度は桁数が足りなくなりがちなので、データは8bitであっても内部演算は16bitとかにしないと精度が保てなくなり、そして16bit演算にするとさらに遅くなるという訳だ。

5 TapのFIRフィルタでこれである。もっとTap数を増やしたり、あるいはさらに複雑な処理(例:FFT)をやろうとしたら、絶対に処理性能が足りない。

そこで、こうした信号処理に向いたプロセッサを作ろう、という機運が1970年代後半から起こりはじめた。実を言えば、こうした処理を1970年代まではアナログ回路で実装している例が多かった。

今から思えばこれは一種のアナログコンピュータなのだが、これをデジタルに置き換えようとしたのがDSPという見方も出来るのではないかと思う。

さて、こういう用途に使うプロセッサとして最終的に出来上がったのは、

・修正ハーバードアーキテクチャ:Program MemoryとData Memoryを分離し、異なるバスで接続することでデータアクセスの際のスループットを確保する

・命令そのものは加算と乗算を高速に行う事が主眼とされる。これをなるべく高いスループットで実行する事が求められる。また命令のLatencyそのものは大きくても許容されるが、Latencyが大きく変化することは許容されない。この結果、命令パイプラインはSuper ScalarやVLIW構成、あるいはSIMDエンジンを組み合わせたものとなる。Out-of-Orderは原則不可(Latencyが大きく変動する可能性があるため)

・継続して同じ処理が繰り返されることが想定される。逆に言えば、様々な処理に向けて分岐が入るような処理はそもそもDSP向けで無い。このため、繰り返し処理を切れ目なく行うための、Zero-overhead Loop機構が実装されることが多い

・バッファに利用するメモリアドレスが通常のリニアのままだと、それを繰り返し利用する場合に「アクセスするアドレスを元に戻す」作業が入る。これを避けるために、Circular Buffer、あるいはCircular Addressの仕組みが用意される

・Data Memoryの方は、外部からのデータ入力の書き込みを行いながら、そのデータを演算部で読み出すという形で同時にアクセスが発生することになる。その際にここがボトルネックにならないように、Dual Port RAMを実装するか、あるいは外部からのデータ書き込みと、演算部からの読み出しでバンクを分けるDouble Bufferingをハードウェアで実装するなどの工夫が施される

といった、通常のCPUとはまるで異なる特徴を持つものになった。

ちなみにここの説明は非常にざっくりしたものであり、実際はもう少し細かい話も色々あるのだが、別に本稿はDSPの原理を説明したい訳ではないので割愛する。

興味ある方は、Analog DevicesのAnalog Dialogue「なぜDSPを使うのか」が判りやすいと思うので、こちらをお勧めする(ちなみにPart 4まである)。

DSP製品の歴史

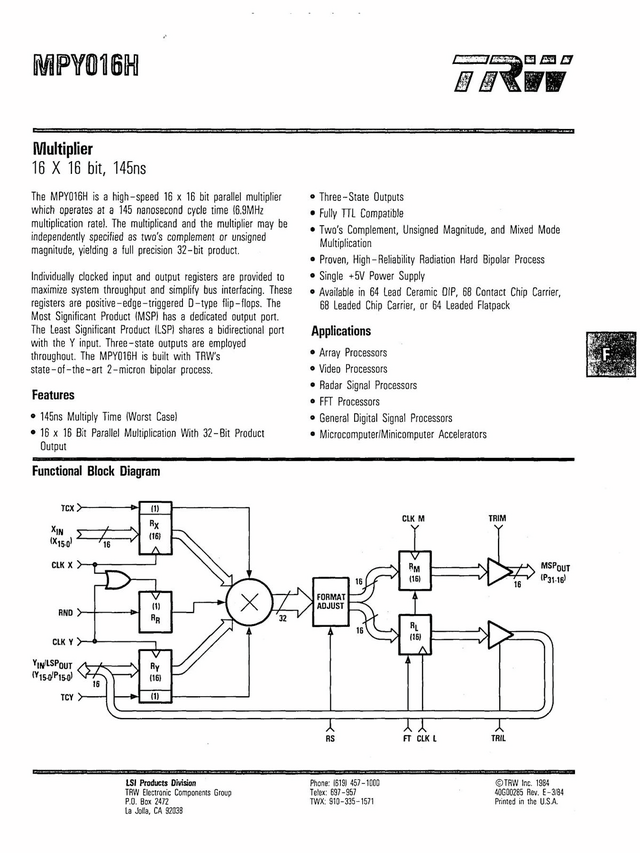

さてそんなDSPであるが、いきなりすべての特徴をもった製品が登場した訳ではない。DSPの歴史で大体最初に名前が挙がるのは、TRWのLSI Products Divisionが1976年に発表したMPY016H(Photo03)で、6.9MHz程の動作が可能だった。

▲Photo03:16bitの値の乗算を行い、結果を32bitで返す「だけ」であるが、それでも当時は画期的だった

当時乗算をこのスピード(1個の演算を145nsで完了する)で実現できたワンチップLSIの製品は他になかった。ただMPY016Hは乗算だけで加算はサポートしていない。乗加算をサポートしたのは、1978年頃に発表されたTDC1010で、16bit同士の乗算結果に32bitの加算を行い、結果が35bitで出力されるものだった。

ただこれはDSPというよりはアクセラレータに近く、プログラムもへったくれもない。X0~X15とY0~Y15という2つの信号ピンに16bitの値を入れると、165ns後に結果がLSP OUT/MSP OUT/XTP OUTという合計35本の信号ピンに値が出てくるだけのものである。

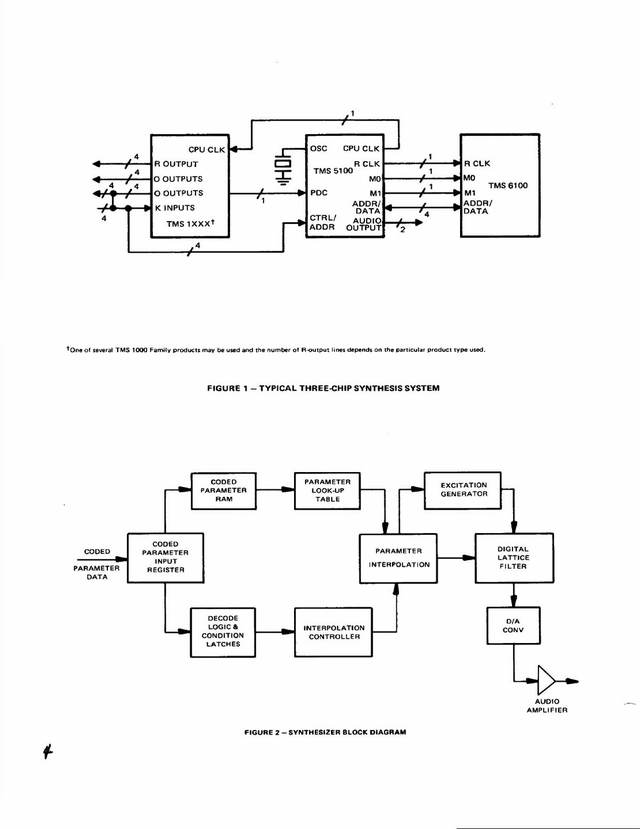

もう少し進化したのが、1976年にTIが開発をはじめ、1978年に完成したTMS5100である。

こちらはTIのSpeak & Spell(これを覚えている方がどの程度いるだろう?)のSpeech Processorとして採用された。

ちなみにTMS5100は商品名で、開発コード名はTMC0280だったので、こちらの方で記憶している方もおられようが、同じものである。

TMS5100はサンプリングレート8kHz/音声帯域4kHzで、49bitの音声データを40Hzで再生することが出来た。TIはこのSpeak & Spellをわずか50ドルで販売している。

DSPを使うことで、高精度かつ高速なな音声処理を低価格に実現できるというDSPの可能性を、目に見える形で示したのがこのSpeak & Spellだった。

ただ内部構造はPhoto04のように3チップ構成であり、また音声合成に特化した構造で、汎用DSPというにはちょっと機能が偏っていた。

▲Photo04:TMS5100自身は10ステージのデジタルフィルタを実装する。TMS6100は音声データのROM、TMS1xxxはコントローラである

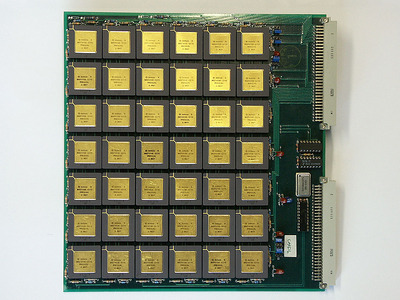

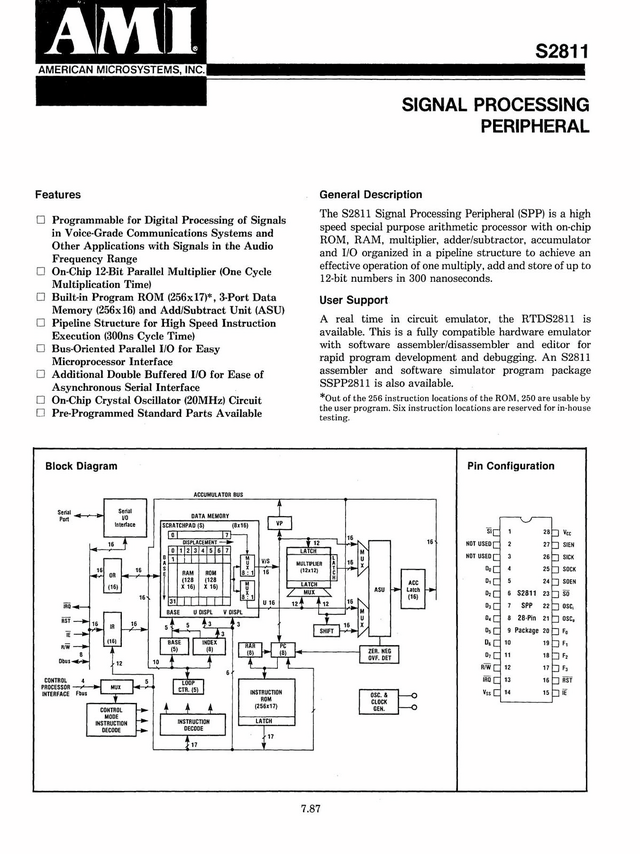

同じ1978年、AMI(American Microsystems Inc,:BIOSで有名なAmerican Megatrends Inc.とは別の会社である)はS2811(Photo05)を発表する。

▲Photo05:Control Modeに入った場合には自分で命令を処理できるし、乗加算の計算方法などもプログラミングは出来るのだが、単体で動作できないあたりが惜しかった

12bit乗算器と加算器が並行で動き、サイクルタイム300ns(つまり3.3MHz駆動)というのは、この当時としては悪くない性能だった。

ただ致命的だったのが、自身でプログラムを実行する機能はなかったことだ。S2811はMotorolaのMC6800などと組み合わせて使う、Acceleratorとしての動作を想定していたからで、結果MC6800に足を引っ張られることになり、性能は芳しくなかったため、ほとんど売れなかった。

1980年に入ると、NECのμPD7720、AT&TのDSP1、Altamira DX-1が登場、この後1983年にはTIのTMS32010が登場し、ここまでが概ね第1世代DSPに属する格好だ。

DSPになりきれなかった異物、Intel 2920

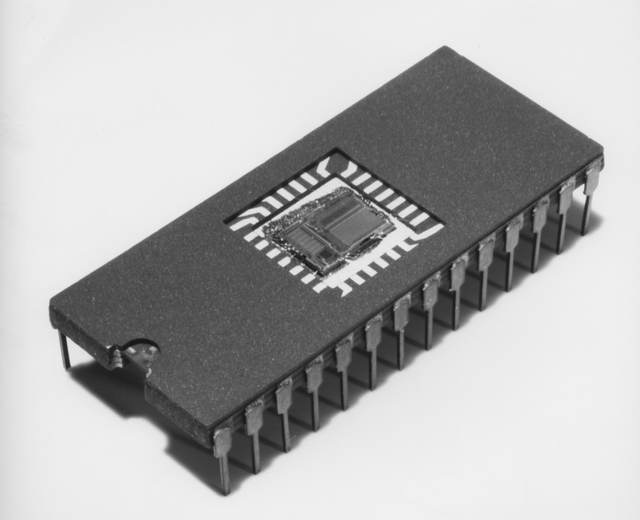

この1980年以降の製品は、ほぼDSPに必要な要素をすべて兼ね備えているのだが、微妙にここに入りきれなかった製品が、今回ご紹介するIntel 2920(Photo06)である。

▲Photo06:黒歴史扱いされて無かったことにされずに、一応IntelのTimelineに名前が挙がっているあたり、表に出ることなく消えた製品が山ほどあるIntelの中ではまだマシな方なのだろう

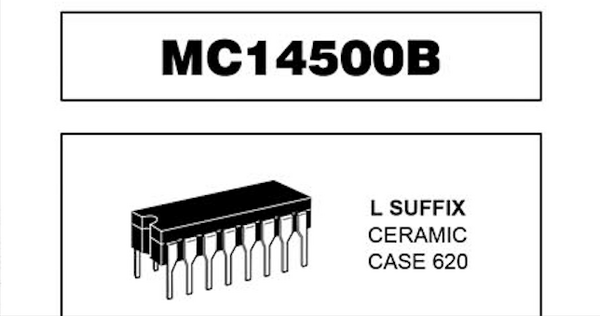

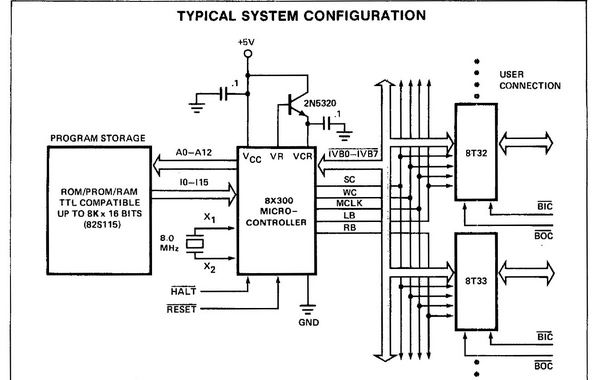

Intel 2920は、ここ(Photo07)にもあるように、Analog Signal Processorであった。

▲Photo07:1980年にリリースされたDesign Handbookの表紙

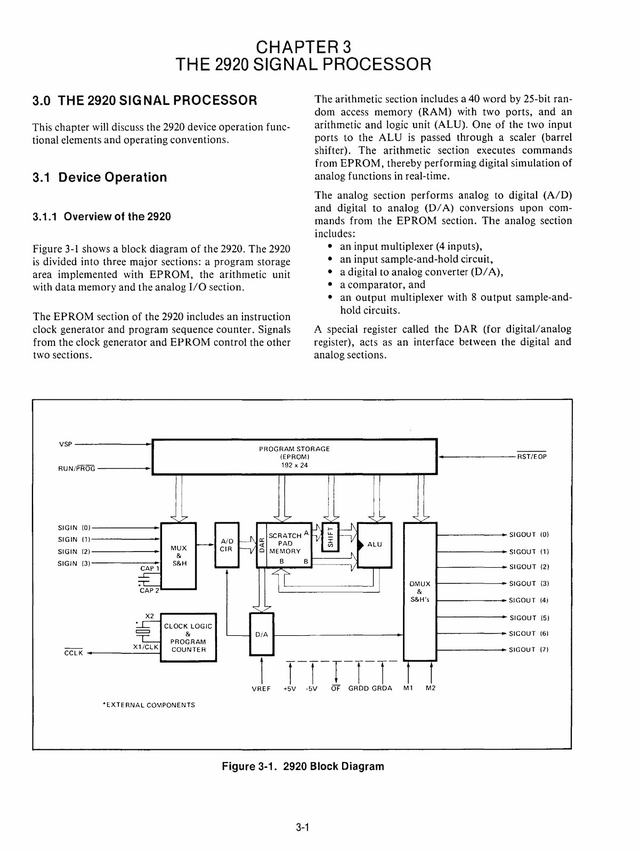

内部構造はこんな感じ(Photo08)。

▲Photo08:なんでMACユニットを入れる発想が出てこなかったのかは不明。別に経験がないわけではないと思うのだが

ADCとDACを内蔵しており、入力信号をそのままデジタル値に変換して処理できるにもかかわらず、そのデジタル処理部には、

・3-tap Low Pass Filter

・Binary Shifter

・25bit ALU

しか存在していない。

一番求められる乗算器は存在せず、しかもそのALUのCycle Time(ALUを実行し、結果をScratch Pad Memoryに書き戻すまでの時間)は400nsで、高速とは言いにくい。

Pipeline動作のLatencyが400nsというのなら別に問題はないのだが、ALUそのものはPipeline構成になっておらず、またWritebackの機能もない。

Intel 2920自身は最大10MHz駆動であるから、要するにALUの実行とScratch Pad Memoryへの書き込みに4cycle掛かっている訳で、これは結構遅い。

ちなみにPhoto08で"DMUX&S&H's"とあるのはOutput Multiplexer & Sample/Holdの意味だが、実際にはAnalog BlockとしてSample/Hold回路やComparatorなども搭載されており、これらの回路ブロックの動作をプログラムから設定することも可能である。

Analog Signal Processorの名前の由来はこのあたりにもあるわけだが、Application Noteを見ると、具体的に、

・22Tapのデジタルフィルタ:115命令

・200Hz~3.2kHzを100Hz刻みでカバーするSpectrum Analyzer、ダイナミックレンジ48dB:155命令

・1200bpsの全二重モデム、送受信フィルタとラインイコライザー機能付き:192命令

といったアプリケーション実装例が示されている。

また様々な特性のフィルタが、Analogブロック+ALUで実装できる例も示されているが、どうもこうした例を見ていると、MACユニットを実装してフィルタリングを全部計算処理でやるよりも、可能な限りAnalog Blockを利用し、その補助にDigital Blockを使うといったやり方の方がコストパフォーマンスが良い、と判断されたのかもしれない。

そしてIntel 2920単体で処理できないような処理は、複数のIntel 2920を連結してPipeline処理を行うことでカバーできる、と判断していたようだ。Transputerの最初のアイデアである、「シンプルなI/Fを経由して他のプロセッサと連携し、スループットがプロセッサ数にリニアにスケールする並列プロセッサ」と考え方は似ている。

あいにく市場はこれを評価しなかった。

そもそも低価格でプログラムを変更するだけで柔軟に信号処理の特性を変えられるというDSPが目指した方向性を考えた場合、複数個のIntel 2920を繋ぐというのは全然低価格に繋がらないからNGだし、Analog Blockでカバーしきれない部分をDigital Block(というか、ALU)で補うという発想は、特性の変更を実装するのに手間が掛かるものになった。

そのALUの性能も決して高くないし、乗算が出来ないのが致命的だった。結局Intel 2920を採用したアプリケーション例はほぼなく、製品は失敗に終わる。

Analog Block取っ払ってALUをMACユニットにし、もう少しスループットを改善すればそこそこ使えるDSPが構築できたようにも思えるのだが、結局IntelはDSPの方向での深堀りを断念し、あっさり撤退する。

その後、Analog Devicesと共同でMSA(Micro Signal Architecture)なるSIMDベースの32bit RISC MCUのアーキテクチャを開発したことを2000年に発表し、Analog DevicesはこのMSAに基づくBlackfin Processorを2001年にリリースする。

このBlackfinベースというかMSAベースのDSPは、2003年にIntelがXScaleベースの携帯向けSoCとして発表されたManitobaことPXA800Fに搭載された。

ただPXA800Fはほとんど採用例がなく(一応O2のXMに採用されたことは判明している)、後継のHermonことPXA900はXScaleビジネスをMarvellに売却したタイミングでキャンセルになった(正確にはMarvellに移管される直前にキャンセルになった「らしい」)あとは、MSAに基づくDSPコアを搭載した製品は、筆者が知る限り存在しない。

Intel 2920の評価としては、NASA/ADSのJ.Heller氏(Communication Systems Research Section)による"An evaluation of the Intel 2920 digital signal processing integrated circuit"という1981年の論文がある。

論文の結論は"The concepts embodied by the 2920 device represent a formidable tool for realizing compact digital filters. The software support is excellent. However, new users should be cognizant of 2920 device problem."(Intel 2920はコンパクトなデジタル・フィルターを実現できる強力なツールである。ソフトウェアのサポートも優秀である。しかしIntel 2920デバイスの問題を認識しておく必要がある)となっている。そのIntel 2920の問題として列挙されているのは、

・ABA命令を正しく動作させるには、4MHz以下にクロックを落とす必要がある

・EOP命令を正しく動作させるためには、21番ピンをOpen-Drain状態にせずに、15pFのコンデンサを繋ぐ必要がある

・22番ピンが正常動作しない

・Reference VoltageとOutput Voltageが一致しない。Referenceが±1Vだと出力は±0.93Vになる。また出力電圧のオフセットも正しくなく、特にLPFアプリケーションを構築する場合に致命的

といったところである。論文によれば評価に使ったIntel 2920はD Steppingであり、2021年夏にE Steppingがリリース予定だが、これで問題が修正できているかどうかは不明、とされていた。

致命的な問題ではない(最後の問題も、3種類の回避法が提示されている)ものの、積極的にIntel 2920を使おうという気分に水を差すには十分な問題ではある。

このあたりも、アプリケーションに採用例がなかった理由の一つかもしれない。