コンピュータの歴史を暗部も含めてていねいに掘り起こすことで定評のある大原雄介さんによる連載7回目。Motorolaといえば、MC6800、MC6809の次はMC68K、MC88K、PowerPC。そこまで記憶している人はそこそこいると思いますが、ColdFireという名前に聞き覚えはありますか?

Motorolaといえば、MC6800→MC6809で8bit CPUのマーケットに大きなシェアを築き、MC68000→MC68010→MC68020→MC68030で32bit CPUのマーケットでも存在感を示したものの、MC68040の開発に手間取り(というか当初仕様を結局実装しきれず)、続くMC68050がキャンセル。MC68060は出荷されたもののあまりに登場が遅く、結局MC68Kのシェアを守ることはできなかった。

その一方で1991年から同社はApple、IBMとAIM連合を結成し、PowerPCコアの開発に携わることになり、これが事実上68Kの後継となった。

こちらはこちらで紆余曲折がいろいろあるのだが、それはともかくとしてこれ以外にもう2つ、MotorolaはCPUコアを手掛けていた。

一つは完全にスクラッチから開発されたMC88K(MC88000)シリーズで、最初の製品であるMC88100は1988年に登場する。ただプロセスが1.5μmのHCMOSでまだトランジスタの実装密度が低く、その一方でMotorolaの設計陣は性能を上げるべく多数の機能と大容量キャッシュを詰め込もうとした結果、MC88100はマルチチップ構成となり、結局性能が出ないという悪循環に陥る。

このあたりの改良を施したMC88110は1992年に登場、だいぶMC88100の欠点は解消されていたものの、もうこの頃になると最初のPowerPCのプロトタイプ(PowerPC 601)が登場しており、しかもMC88110よりも高速だった。

MC88Kでもなく、PowerPCでもない、Motorola第3のRISCコア

結局MC88100は僅かな数量出荷されただけで市場から消えている。このMC88Kも、これはこれでマイナーCPUの題材としても面白いのであるが、何しろ2製品しかないし、実質MC88100しか市場に出てないようなものなので、ちょっと見送り。88Kの話は拙著「忘れ去られたCPU黒歴史」をお読みいただきたい。

今回取り上げるのは、そのMC88Kと並行してMotorolaが開発していた、ColdFireである。

ColdFireは1995年に発表された、RISCベースのプロセッサアーキテクチャである。2006年の時点での説明では、

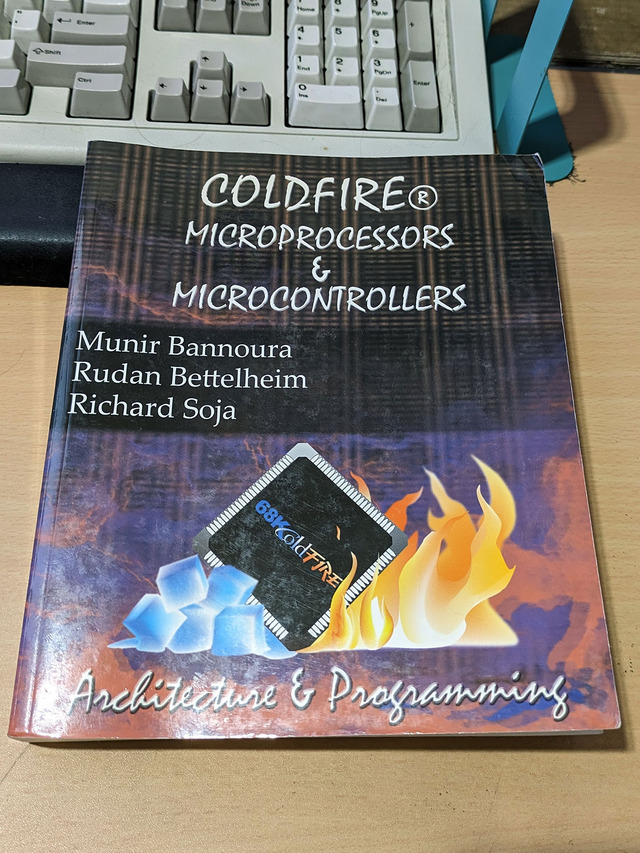

ColdFire V2:1+1 Stageのシングルパイプライン

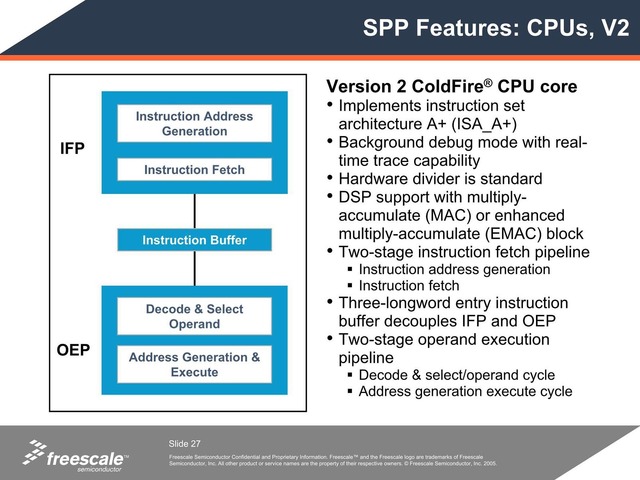

ColdFire V3:4+2 Stageのシングルパイプライン+ローカルバスのパイプライン化

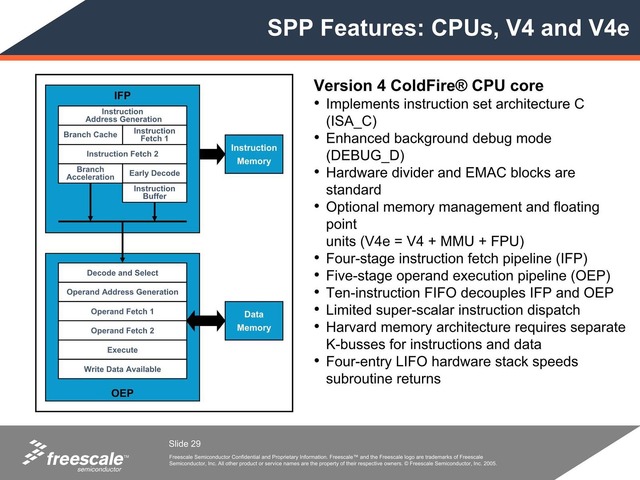

ColdFire V4:4+5 Stageの、限定的なスーパースケーラ

ColdFire V4e:ColdFire V4+FPU+MMU

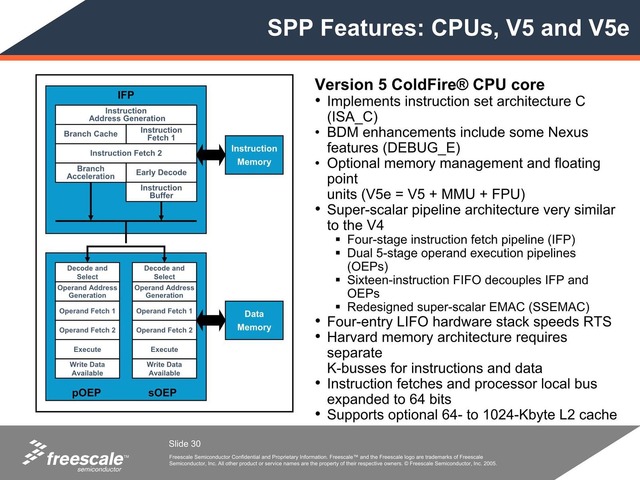

ColdFire V5:V4の完全スーパースケーラ化

ColdFire V6:スーパーパイプライン化

ということになっている。ColdFire V1はないのか?というと、実は存在した。このColdFire V1は1993年頃にMotorola社内で初めて開発されたそうなのだが、どうも性能が出なかったそうで、そのままお蔵入りになったらしい。

その後、改めて開発し直したのが1995年のColdFire V2という訳だ。ちなみに後述するように、この後でColdFire V1が改めて追加されるが、これはいわばColdFire V2の縮小版で、元々のColdFire V1とは異なるものである。

さてそのColdFire、基本的なアイデアは「68Kの命令セットを利用したRISCプロセッサ」である。もっともご存じの通り68Kの命令セットというのは直交性の高い、典型的なCISCのものである。x86はこれを「RISC風の内部命令に変換して実行する」という形で克服したが、ColdFireは割と愚直に実装している。この結果、「可変長命令に対応したRISC」という、あまり例のない構成になっている。

全然例がないという訳でもなくて、例えば台湾RDCは80186/80188互換のRISCプロセッサであるR8800シリーズを提供しているが、これは元が8086の命令セット+αだから、当然可変長命令ということになる(RDCのR8800の話は以前こちら こちらでちょっと触れた)。

話を戻すと、この可変長命令のRISCプロセッサという構成について、"ColdFire Microprocessor & Microcontroller"(Photo01)の冒頭では"The ColdFire family combines both benefits of CISCs and RISCs worlds by providing a variable-length reduced instruction set(RISC)architecture and keeping the same architecture that most engineers are familiar and comfortable with, but offering a much higher performance than CISC."と能天気に締めくくっている。

▲Photo01:AMT Publishing出版のこの書籍、一般には流通していない。筆者は、最後のFTF(Freescale Technology Forum)の折に、会場で販売していたものを購入。一応米国Amazonで古本として販売されてはいる

とはいえ、流石にMC68Kに100%命令互換となると実装が大変なため、いくつかのアドレスモードやデータフォーマット(例えばBCD Packed)、余り使われない命令を廃止するなどして簡単化はされている。ただ主要な命令はほぼそのまま実行可能となっている。もっとも命令互換といってもそれはアセンブラレベルの話で、バイナリベースでの互換性はない。

さて、このColdFireの最大の特徴はそうした命令セットよりも、実行パイプラインの構造にある。

前出の"ColdFire Microprocessor & Microcontroller"によれば、"All ColdFire cores includes two independent and decoupled pipeline: an instruction fetch pipeline to prefetch instructions and an operand execution pipeline that performs the actual instruction execution. The two pipelines are connected via an instruction buffer, which serves as a FIFO buffer"と説明がある。

「何で」分離したか、の説明が皆無な辺りがアレなのだが、実際にColdFire V2~V5のパイプライン構造(Photo02~05)を見ると、どれもこれも綺麗にフロントエンドとバックエンドが分離しているのが判る。

▲Photo02:ここからPhoto05までの出典は、2006年のFTF(Freescale Technology Forum)で行われた"ColdFire Platform Architectures,Peripherals, and Trends(AE112)"というセッションの資料。ColdFire V2だとIFP/OEPはそれぞれ1 StageのPipelineである

▲Photo03:ColdFire V3。IFPがかなり高度化。OEPも2 Stage Pipelineに。

▲Photo04:ColdFire V4。OEPが5 Stageに。またIFPもさらに高度化し、分岐予測ユニットが大幅に強化

▲Photo05:ColdFire V5。遂にSuper Scalar化

何でこんなことに、というのは以前から考えて居たのだが決定的な解は判っていない(MotorolaというかFreescaleの関係者に尋ねたこともあるのだが、明快な回答は得られなかった)。

ただ可能性の一つとして考えられるのは、先にも書いたようにColdFireの命令セットは可変長である。なので、IFPの出力と言うのは毎cycleごとに得られるとは限らない。1cycleでデコードされた命令が出てくる場合もあれば、3cycle掛かることもある。この差を吸収するために、FIFOを挟もうというアイデアの可能性はある。

ただ、それはIFPとOEPが単に"Decouple"なだけでなく、別々の動作周波数で動くくらいのことをしないと本当の意味での効果は無い気がするし、同じ動作周波数で動くなら単にInstruction Fetchの後ろにFIFOを入れて1本のPipelineでいいのでは?という気もしなくはないから、決定的なものとは言えない。

理由はともかく、この分断された独立のPipelineというのがColdFireの最大の特徴、と言えなくもない。ちなみに上のリストで書いた1+1 Stageとか4+5 Stageというのは、IFPとOEPのそれぞれのStage数である。

MotorolaとしてはこのColdFireで、既存のMC68Kのマーケットをそのまま継承していきたい、と考えていたようだ。構造の特異さはともかくとして性能として公表されていた数字で言うと

ColdFire V2 : 25MIPS@33MHz 50DMIPS@54MHz

ColdFire V3 : 70MIPS@90MHz 200DMIPS@240MHz

ColdFire V4 : 510MIPS@333MHz 410DMIPS@266MHz

ColdFire V5 : 610MIPS@333MHz (DMIPSは未公開)

といったところで、ここから計算すると

ColdFire V2 0.8~0.9 DMIPS/MHz

ColdFire V3 0.9~1.0 DMIPS/MHz

ColdFire V4 1.5 DMIPS/MHz

ColdFire V5 1.8 DMIPS/MHz(推定値)

といった値になる。MC68Kシリーズの場合、

MC68020 4 DMIPS@20MHz = 0.20 DMIPS/MHz

MC68030 11 DMIPS@33MHz = 0.33 DMIPS/MHz

MC68040 44 DMIPS@40MHz = 1.10 DMIPS/MHz

MC68060 88 DMIPS@66MHz = 1.33 DMIPS/MHz

といった数字だから、性能的には十分後継製品に相応しい数字である。

一番簡単なColdFire V2ですらMC68030を超える性能であり、これをベースにMCUやMPUを構築するには十分な能力と言える。ただMotorolaというか、途中から半導体部門は分社化してFreescaleになった訳だが、ColdFire V2とV3はMCU向けに、V4以降をMPU向けに割り当てるつもりだった。

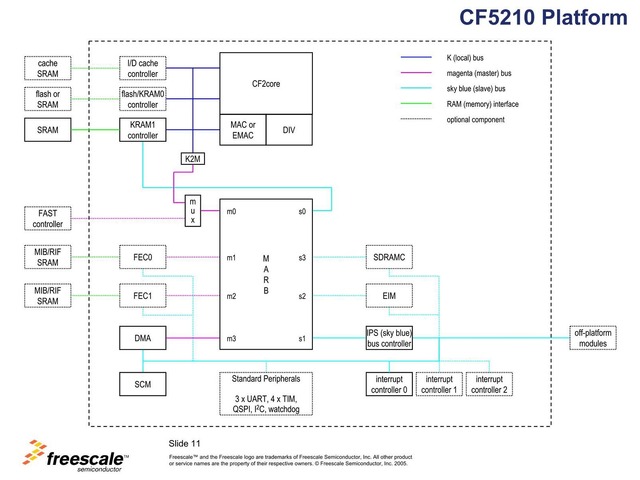

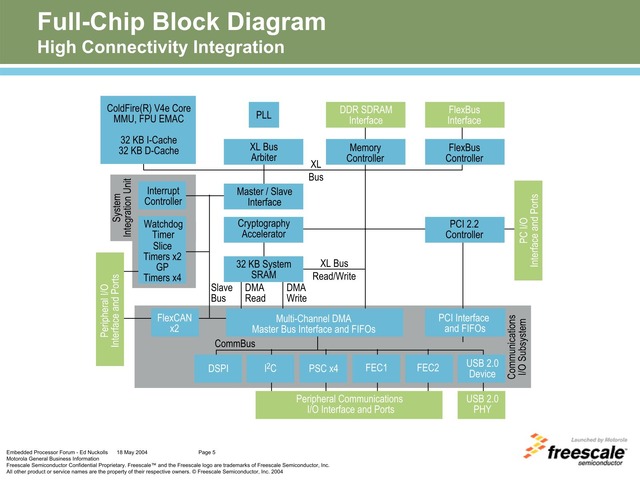

ColdFire V2をベースとしたMCUの構成例がこちら(Photo06)で、ColdFire V4をベースにしたMPUの構成例がこちら(Photo07)である。

▲Photo06:FECはFast Ethernet Controller(10/100BASE-T)、EIMはExternal Interface Module、中央のMARBは周辺機器用のSwitchである。CF5210というのは、Freescale内部でのプラットフォームの型番で、これがそのまま外部に提供されていた訳では無い模様

▲Photo07:これはEmbedded Processor Forum 2004で公開されたもの。ColdFire MCF547xというネットワーク向けプロセッサである

この当時、というのは2004年~2005年頃という話であるが、例えばNetwork向けであれば、簡単なEndpointをColdFire V2ベースで、その先のモデムやゲートウェイをColdFire V4/V4eベースで構築し、アクセスポイントとかはPowerPCとかPowerQUICC(PowerPCに通信向けの周辺回路を搭載した製品。QUICCはQUad Integrated Communications Controllerの略)やPowerQUICC II/IIIでカバーするというロードマップが示されていた。

当時の腹積もりでは、より高い性能が求められたらColdFire V2をV3に、V4/V4eをV5にシフトさせることで、ソフトウェア互換性を保ちつつより高性能が実現できる、というあたりだったのだろう。

市場から見捨てられた互換性

生憎と、そういう風にはならなかった。最大の問題は、割と早いタイミングで顧客はMC68KからPowerPCやARM(Arm)、MIPSなど他のプラットフォームに移行してしまい、MC68Kへのソフトウェア互換性が要求されるマーケットが殆ど無くなってしまったことだと思う。

何しろMC68Kの開発元であったMotorola/Freescaleが早々とPowerPCへ軸足を移してしまったことで、多くのベンダーが必然的にMC68Kを捨てることになったからだ。

先のPowerQUICCにしても、元々はMC68000コアに通信機能を搭載したQUICCことMC68300シリーズとして市場投入されており、このコアをColdFireに切り替えていればまだ生き残りが図れたのかもしれないが、これを早々にPowerPCベースに移行させてしまった以上、ソフトウェア互換性があっても市場はもう残っていない。

同様にハンドヘルドデバイス向けに投入していたDragonBallことMC68328や、その後継のDragonBall EZ/DragonBall VZというコアはMC68000ベースの製品で、Palmに使われたことで有名だが、後継であるDragonBall MXはARMベースになってしまい、ここでもColdFireに出番は無かった。

このあたりでFreescaleもColdFireをだんだん持て余し始めたらしい。2005年頃の同社の説明によれば、ASICのコア向けとか「Emerging Market」向けとかいう説明になってきており、作ったは良いもののどこに売ったものか、という感じが見て取れる。

2007年に同社が発表したFlexisシリーズも、今から思えばそうした模索の結果と思えなくもない。Flexisというのは、8bit MCUのS08ベースのコアと、ColdFire V1(これはColdFire V2のサブセット版として新たに開発されたもの)ベースの32bit MCUをセットにした構成で、開発プラットフォームと周辺機器、パッケージなどを完全に互換にした。要するにエントリー向けにはS08で開発を行い、より性能が必要な場合はColdFire V1に差し替えるだけで済むというものだ。勿論ソフトウェアというかバイナリの互換性は皆無だが、開発ツールレベルでソースコードの互換性を保つ(勿論アセンブラではなく高級言語レベルだが)ようにしたことで、移行を容易にする、というものだ。

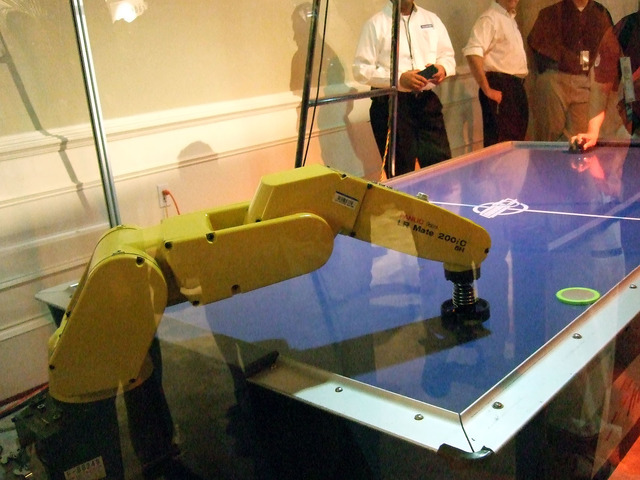

デモではエアホッケーの操作システムを構築し(Photo08)、S08ベースだと人間が楽勝で勝てるのに、ColdFire V1に差し替えると人間がまるで手が出ないレベルまで強力になるといった形で性能をアピールしていたが、2007年というのは既にARMがCortex-M3をリリースした後であり、この後MCUのマーケットは急速にARMベースに置き換わっていく。

▲Photo08:これは2008年のFTFでの風景。エアホッケーの台の上にカメラが設置され、そのカメラでパックの位置を判断。プッシャーが装着されたファナックのロボットアームを制御し、パックを打ち返すというもの

結局Flexisシリーズはマーケットシェアを握ることが出来ず、それどころかFreescale自身が2010年にKinetisというCortex-MベースのMCUのラインアップを揃えたことで、むしろ更に追い込まれる始末である。

2011年頃に、FreescaleでMCUのマーケティングを統括していたJeff Bock氏(故人)に話を聞いたことがあるのだが、この時点でColdFireのポジショニングは「特定分野向けASSP用」という返事であり、またColdFire V5はまだこの時点で投入時期が決まらないとしていた。ColdFire V6は開発は続いているものの、アナウンスできる話は無い、という返事だった。

結局ColdFireは2010年に90nm TFS(Thin Flash Storage:Freescale独自のフラッシュメモリ用プロセス)に対応したColdFire+という製品を最後に新たな展開や製品が投入されることなく、Flexisシリーズのフェーズアウトに合わせる形で市場から消えていった。一つの理由は、Motorola/Freescaleが手を広げ過ぎたことだ。

Motorolaの時代もMC68K、MC88K、PowerPC、ColdFireと4つものアーキテクチャを同時開発していた訳で、そりゃ開発の手が回らない=製品投入が遅れるのも無理はないし、Freescale時代はPowerPCとARMに注力していたから、やっぱりColdFireに注げる開発力はそう多くなかった。

もっとドラスティックに、例えばMC68050のキャンセルのタイミングでMC68060も中止して浮いた開発リソースを全部ColdFire V4に突っ込むとかしていれば(そしてMC68040後継のColdFire V4ベースのプロセッサをリリースすれば)また違った展開もあったかもしれないのだが、そうした決断が下されることはないまま、ひっそり消えていったのはちょっと可哀想ではある。