コンピュータの歴史を暗部も含めてていねいに掘り起こすことで定評のある大原雄介さんによる連載13回目。今回取り上げるのは前回のSigneticsが製造を担当した、SMSのSMS300および8X300です。

前回の記事の冒頭でちょっと触れた8X300が今回の主役である。

SMSことScientific Micro Systemsとはどういう会社だったのか?

元々この製品は、SMSことScientific Micro Systemsという企業で設計され、ただし製造をSigneticsが全面的に受託したという変な経緯を持つプロセッサだ。Scientific Micro Systemsという会社、同名の他社が多数存在するので非常に判りづらいし、創業時期も複数あって混乱するのだが、どうも1969年創業というのが正しいらしい。

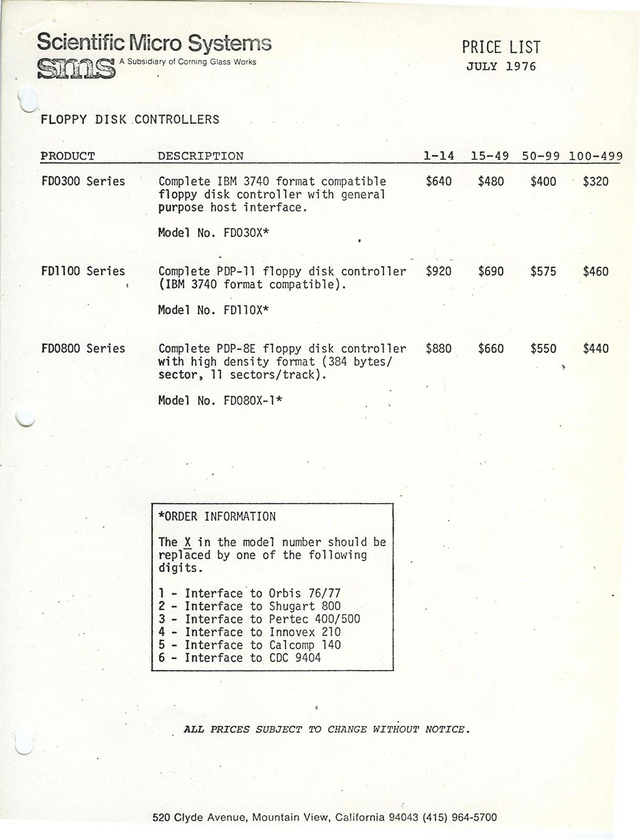

もっともこの創業ってなんだ? という話もある。というのはこのScientific Micro Systemsは独立の会社ではなく、(前回も出て来た)Corning Glassの子会社だったらしいからだ。Photo01は同社の1976年7月付の価格表だが、"A Subsidiary of Corning Glass Works"と左上に明確に記されているのが判る。

で、この当時の同社の主力製品は間違いなくHDDのコントローラだった。GDCAという「廃番になってしまった製品を(オリジナルのメーカーに代わって)長期供給する」ことをビジネスにしているメーカーのカタログを見ると、まぁいろんなコントローラ類が並んでいるのが判る。

HDD/FDDのコントローラだけでなく、非同期シリアルインタフェース(DHV11-Jの名前が挙がっていていろいろ感慨に耽ってしまった)などもSMSの代替品としてリストアップされていたあたり、要するにミニコン向けの周辺機器を扱うメーカー、という位置付けが一番正しいと思う。

ちょっと後になるが、1987年にはSMSがサンディエゴのLevcoという、Macintosh向けの周辺機器を扱っていた企業を買収したことを1987年8月12日付のLA Timesが報じており、この中でSMSのことを"publicly held computer peripherals company based in Mountain View."とし、また1986年度の売上が6500万ドルだったと報じてるあたり、どこかのタイミングでIPOしたものと思われる。

冒頭に「創業時期が複数ある」と書いたが、ひょっとすると1976年創業となっているのは、1976年にIPOをしたからかもしれない。また1990年代にSanDiskに在籍しておられたDaniel Auclair氏(当時の肩書はSVP, Operations & Technology)の経歴が"1988年までSMSのVP兼OMTI部門のGM"となっている(これはSanDiskの1996年のForm 10-Kに示されている)ことから、少なくとも1988年頃までは同社が存続していたことは間違いない。

あと1989年10月24日にSCSI Host Adapterに関するFCCの認可を取得しているため、この辺までは会社があったものと考えて良さそうだ。ただこの後同社の消息はさっぱり判らなくなっている。

ついでに言えば、"Corning Glass Works"で調べるとこんなものが引っかかってくる。元のレポートは1976年発行だから、まさにSMSでSMS300を開発していたころの話である。なんかこう、いろいろあったんだろうなと推察される。

SMS300のアーキテクチャ

さて、そんなSMSがなんでまたCPUを開発していたのか? に関する公式の説明は無いが、SMS300の内部構造を見ていると当時同社の主力製品だったHDDのコントローラを構成するために高速なプロセッサが必要であり、手頃なものが無いので自前で作ろう、と考えたのではないかと思う。

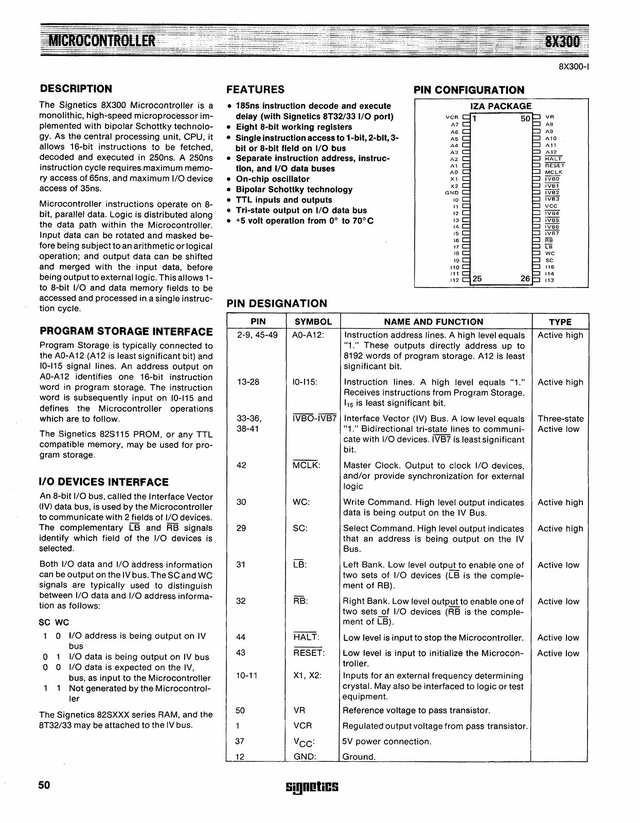

そんなSMS300であるが、いろいろ突き抜けているというか極端である。データシートのトップページ(Photo02)を見ると、

製造プロセスはBipolar(つまりNMOSもPMOSでもない)。

実行サイクル(後述)は僅か250ns。つまり250nsで全ての命令が実行できる。

パッケージは50pin DIP(これもかなり珍しい)。

アドレスバスは13bit、命令バス(Instruction Line)は16bit、I/Oバス(Interface Vector:IV Bus)は8bit。要するにROMなりRAMなりを接続する命令バスと、外部入出力を行うI/Oバスが分離されている。

と、この時点で既になかなか尖った特徴がいくつか見えてくる。

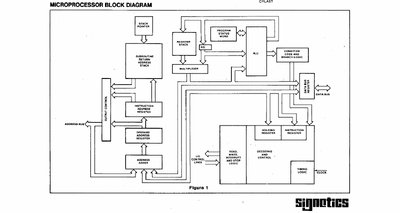

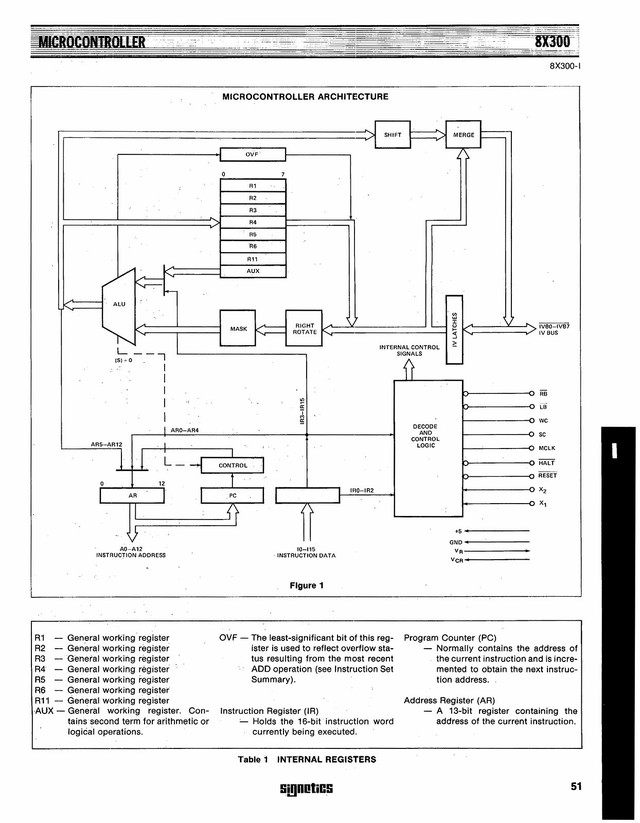

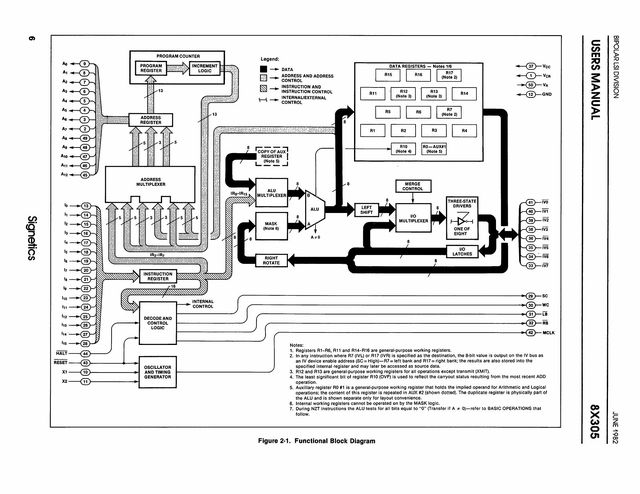

内部構造はこんな感じ(Photo03)。

汎用レジスタはR1~R6+R11にAUXまでいれて8つで、他にAR(Address Register)/PC(Program Counter)/IR(Instruction Register)の3つと、読み出し専用のOVF(OverFlow)レジスタが用意される。OVFは直前の加算命令の結果がオーバーフローになった場合、LSBが立つ(あとは全て0)という構成である。

さて、なんでアドレスが13bitか? に対する逆説的な説明になるが、SMS300の命令フォーマットは16bitであり、うち先頭3bitがOpCode、残り13bitがOperandである。つまりこのOperandに収まるようにしようとすると、Addressは13bitに収めないといけないという訳だ。

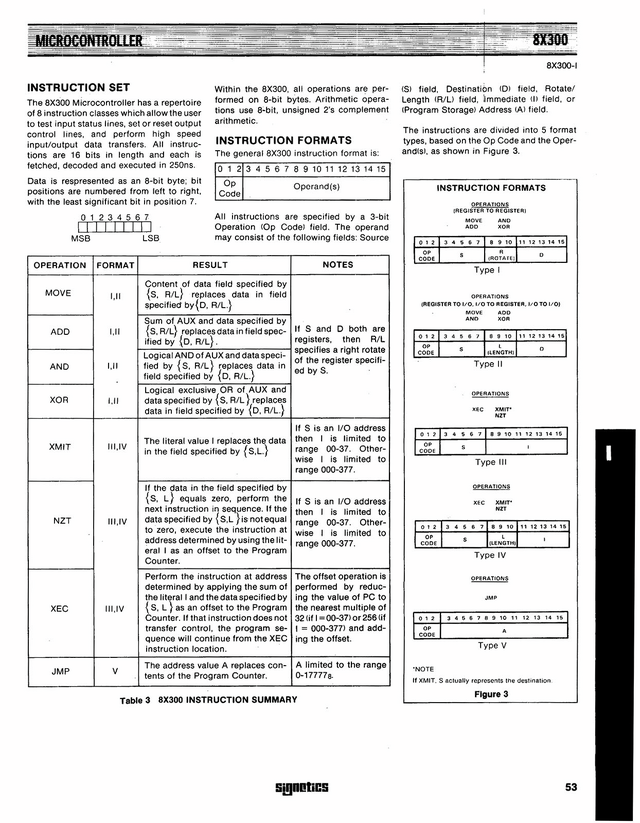

さて、OpCodeが3bitということは、つまり命令は8つしかサポートできないことになる(Photo04)。

実際あるのはMove(IVとレジスタの間でのデータ交換)、ADD/AND/OR/XEC(IVないしレジスタの値とAUXレジスタの値でAdd/AND/OR/XORの計算を行い、結果をIVないしレジスタに戻す)、XMIT(8bitの即値をIVなりレジスタに格納する)、NZR(指定されたIVないしレジスタの値が0/非0かで、次の命令ないしPC+オフセットのアドレスにジャンプする)/JMP(絶対アドレスへの無条件ジャンプ)の8命令だけである。

算術演算命令がADDだけ、というあたりに猛烈な潔さを感じるかと思うが、要するに計算というよりもコントローラ的な用途に向けたCPUだと思えば納得できる。データの処理とかは考えておらず、もうひたすらホストから来たデータをHDDに書き出す(あるいはHDDから読んだデータをホストに送り出す)ことに注力した仕組み、と考えれば良い。

もうちょっと後の時代ではこうした処理はDMAで行う(つまりCPU外部にデータ転送専用の処理ユニットを置き、ここがCPUとは無関係に転送処理を行う)形になるのだろうが、1970年代のしかも低価格なコントローラ向けの用途では、CPUをブン回した方が合理的という考え方は理解できる。

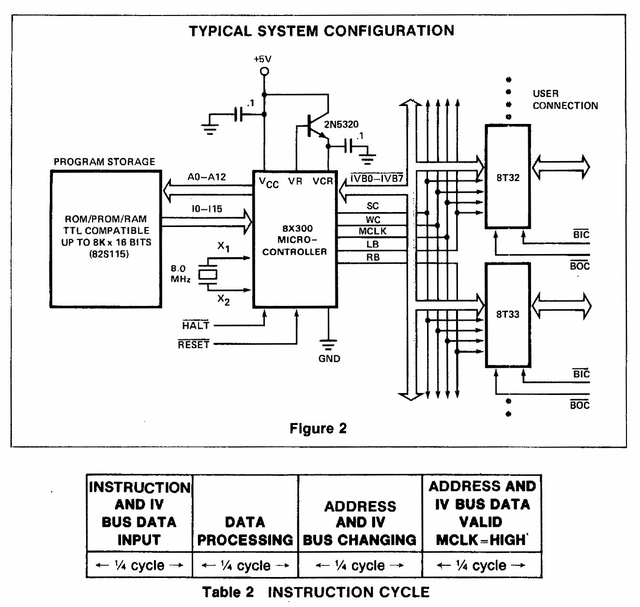

ところでPhoto05はTypical System Configurationであるが、何か気が付いたことは無いだろうか?

いや、先ほどの命令セットの説明でも気づかれた方はいるかと思うが、「SMS300は、CPUからRAMに書き出すことが一切出来ない」。少なくともInstruction Busを使う限り、Memory→SMS300の一方通行であり、書き出す方法が明示的には無いことになる。

ということは、例えば自身でカウンタを制御したいという場合、汎用レジスタのどれかをカウンタ用に充てるか、もしくはIVの先に何かしらRAMに当たるものを用意しておき、ここを読み書きするしかない。

割り込みラインも無い(しいて言えばReset?)し、あったところでStackも無ければcall/returnの仕組みも無いから、割り込み処理は不可能である。

多分これにRTOS載せようとしたら、開発者が頭をかきむしって悩むことになりそうだ。CPUというよりもDSPに近いもの、と言っても良いかもしれない。

その一方で、Photo05下のTableにあるように、1cycleで命令のFetch、データ処理、書き出し先確定、出力まで完全に行える。外部クロックは8MHzだが、内部ではこれを2分周して4MHz駆動(Cycle Timeが250ns)で動いている関係で、実質的に4MIPSの処理性能が実現できる(IVなりProgram Storageがこれに間に合えば、だが)。

外部出力はIV経由だが、このIVはアドレス/データ多重になっており、更にLB/RB(Left Bank/Right Bank)の信号線を使うことで、最大512ポートを利用可能になっている。

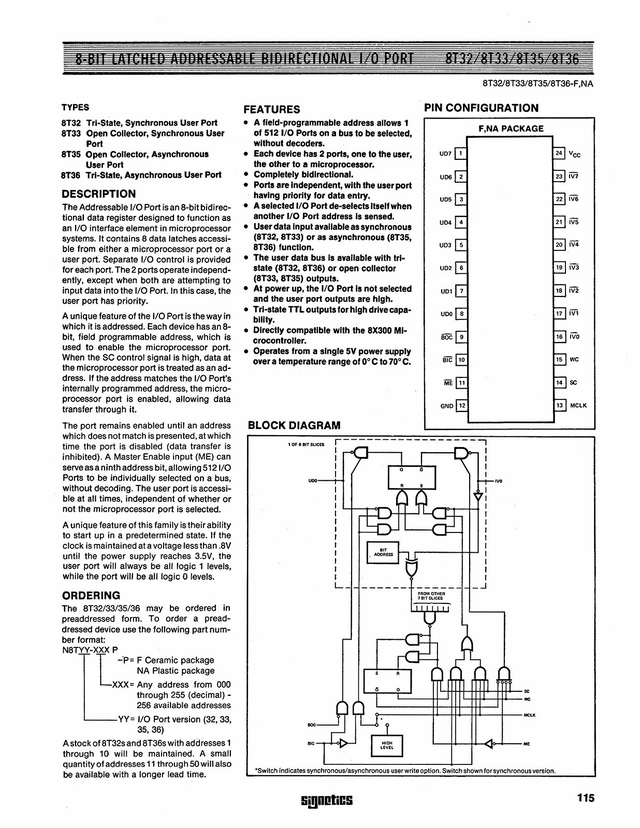

Photo05でBT32/BT33とあるのはアドレス制御付きラッチ(Photo06)で、だから最大構成ならこれを256個づつLB/RBに分けてぶら下げることで、512個までのデバイスを接続できることになる。

Application Noteとしては、

Floppy Disk Interface

Teletype Multiplexer

Data Concentrator

Remote Alphanumeric Terminal Controller

Computer I/O Bus Emulator

Interface to External Read/Write Memory

CRT Controller

などの実装例が示されている。概ねこういった用途向けを狙った、というかこういう用途にしか使えないのがSMS300だった訳だ。

お茶目(?)なポイントとしては、5V単一電源と言いつつ、実施には内部でもう少し低い電圧を必要とする関係で外部にレギュレータ回路が必要なところだ。

Photo05で5Vから2N5320を経由してVCR(Regurated output voltage)を入力しているのがそれだ(ベースに入るVCはReference voltage)。

この辺は、ICの設計に慣れてないSMSの苦心の様を見るようだ。

さて先に書いたようにSMSは半導体ではなくそれを利用した装置を製造・販売するメーカーだったから、設計はともかくとして製造はどこかに委託する必要があった。

そこでセカンドソースと言いつつ、実際にはファーストソースも無ければ他に生産した会社も無かったので、事実上SigneticsのみがSMS300の製造を受託、1976年に出荷開始された。

当初は8MHz駆動が難しかったようで6.66MHz(つまり内部的には3.33MHz)駆動だったが、すぐに4MHz版が登場している。機能は限られているし、バイポーラでの製造だからNMOSのCPUに比べれば多少消費電力は大きかっただろうとは思うが、同時期のCPUでは実現し得ない高い処理性能(≠演算性能)を発揮したことで、意外にこの製品は広範に使われた。

SMS300から8X300へ

70年代後半~80年代のHDDのコントローラとして広く採用された。そんな訳で好調な売れ行きだったためだろうか? SigneticsはSMSからSMS300の権利を全て買収、8X300と改称の上、自社ブランドでの販売に切り替えている。

そして1982年、Signeticsは8X300の改良型として8X305を発表する(Photo07)。

外部クロックは10MHz、つまり内部5MHz駆動になった。また命令そのものは8X300と後方互換性を維持しつつ、汎用レジスタはAUX以外にR0~R17まで16個(相変わらずOctal)が用意されたほか、新たにR7をLeft Bank Register、R17をRight Bank RegisterとしてIV出力の際に特定の意味を持たせたり、ADD命令の際にShift&Mask/Rotate&Maskの機能が追加され、Bit処理がより容易になった。

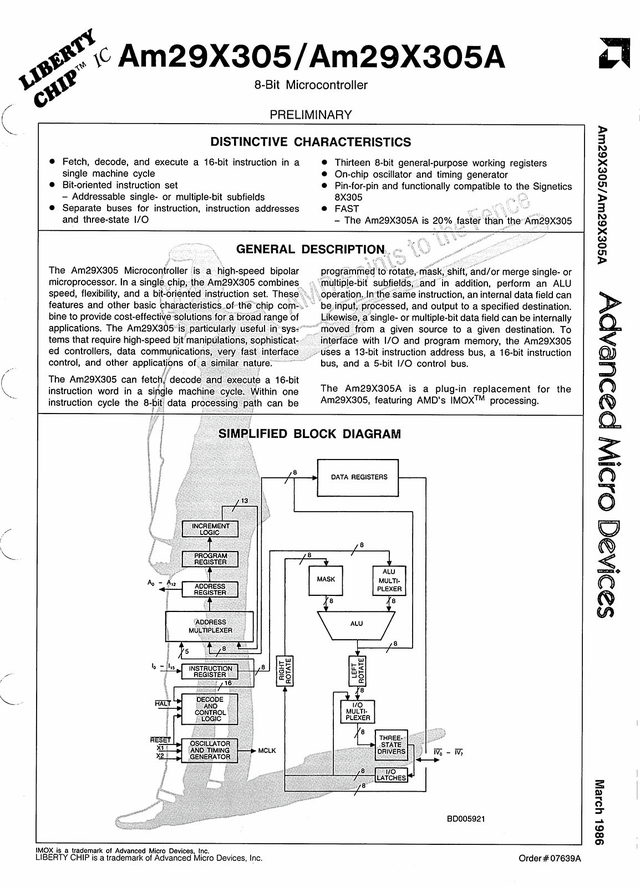

パッケージは引き続き50pin DIPの形であるが、後追いで68pinのPLCCも追加されている。この8X305はAMDからもセカンドソースとして提供された(Photo08)。

この8X300や8X305はHDDだけでなく、特に軍用で広範に採用されてしまったために、Signeticsというか親会社のPhilipsも簡単に生産を終了できなくなった。そこで1990年代に8X305は、やはり生産終了した半導体の長期供給を行うLansdale Semiconductorに移管され、SL8X305という名称で現在も供給されている。

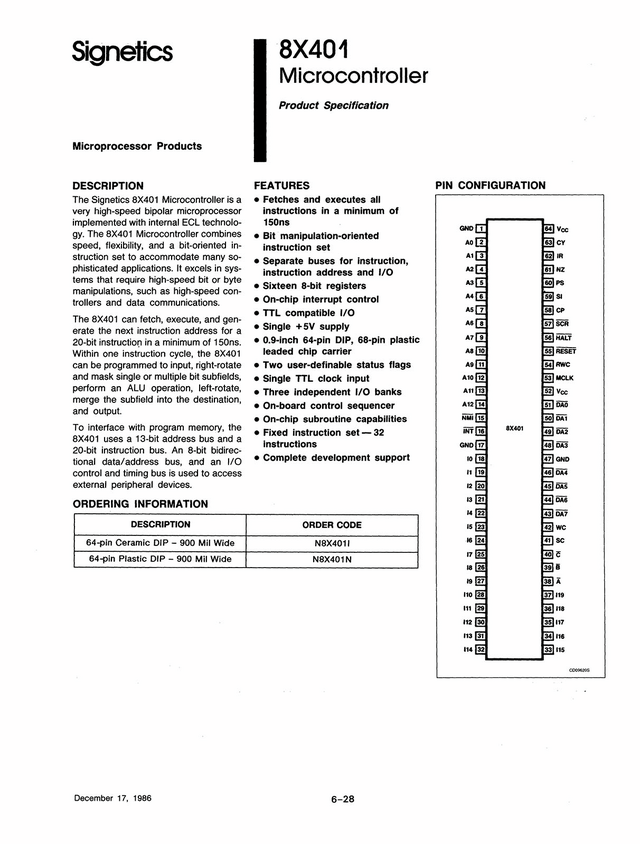

さてこの大ヒットに気を良くしたのだろうか? Signeticsは8X401を1986年に発表する(Photo09)。

最大の違いは命令セットの拡張である。Photo09にもあるようにInstruction Bus幅は20bitになった。要するに命令長が20bitになった訳で、OpCodeは4bitになった(このままだと最大16命令だが、実際にはOpCode以外のフィールドも利用することで最大32命令を定義)ほか、汎用レジスタも32個に強化。

また割り込みラインが追加され、これに伴いJump/Return命令がかなり強化されている。Cycle Timeは150nsまで短縮されており、8X305比で35%高速とかいう話であった。

残念ながらこちらは全然成功しなかった。割り込みをサポートするということはISR Call/Return的動作を可能にしている訳だが、流石にこうしたものをサポートするとなると汎用レジスタだけではいろいろ足りず、どうしても外部にSRAMなりDRAMが欲しくなるが、8X401は相変わらずDRAM/SRAMを使いたければIVの先に置くしかなかった。

また1970年代には超高速の部類に入った処理性能も、1980年代後半になるとDSPの出現などでそれほど性能面でのアドバンテージは無く、むしろ「使いにくいMCU」というネガティブな面が強調されることになってしまう。

いろいろ構造を変えた結果として、8X300/305とのソフトウェア互換性が失われたのも痛かった。こうした理由で、8X401は8X300程の成功を収めることも適わず、あっさり市場から撤退していった。

DSPが市場に出てくるまでの繋ぎとして活用されたのが8X305で、DSPが出たからもうお役御免になってしまったのが8X401というあたりか。

余談だが8X300は、なぜかソビエトで大人気だったらしい。Soviet ElectronicaはKM1818VM01Aという型番で8X300のクローンを(もちろん勝手に)製造しており、新品ではない(と思うのだが)もののまだ購入できる(その例)。まぁ買ったからといってどうしようもないのだが。

あと説明が"8bit RISC-like CPU"だが、これを果たしてRISCと呼んでいいものかどうか。確かに命令数は少ないが。